射频集成电路在现代无线通信、雷达和物联网等领域扮演着核心角色。其中,横向扩散金属氧化物半导体(LDMOS)因其高功率、高效率和高线性度等优点,已成为射频功率放大器的主流器件之一。随着工作频率的提升和电源电压的加大,LDMOS的击穿问题日益凸显,直接影响电路的可靠性和寿命。因此,设计适用于射频集成电路的抗击穿LDMOS至关重要。本文将探讨其设计原理、关键技术和优化策略。

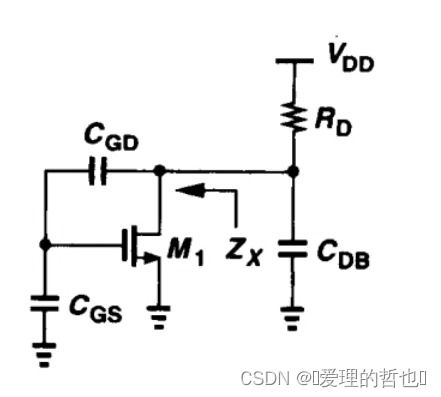

理解LDMOS的击穿机制是设计的基础。击穿通常分为两种类型:雪崩击穿和热载流子击穿。在射频应用中,高电压摆动可能导致器件内部电场集中,引发雪崩倍增效应;高频操作下,热载流子注入栅氧化层会降低器件稳定性。抗击穿设计的核心在于优化电场分布,降低峰值电场强度。这可以通过调整器件结构参数实现,例如增加漂移区长度、采用阶梯掺杂或RESURF(降低表面电场)技术。RESURF技术通过引入轻掺杂漂移区,使电场在水平方向更均匀分布,从而提升击穿电压。实验表明,合理应用RESURF可将击穿电压提高30%以上。

工艺优化是抗击穿设计的关键环节。在射频集成电路中,LDMOS常与CMOS工艺集成,因此需兼容标准流程。关键工艺步骤包括栅氧形成、离子注入和金属化。为增强抗击穿能力,可采用厚栅氧设计以减少电场穿透,但需权衡与射频性能(如跨导)的平衡。优化漂移区掺杂轮廓至关重要:通过多次离子注入形成渐变掺杂,可平滑电场峰值。例如,采用磷或砷的倾斜注入,能有效缓解结边缘的电场集中。表面钝化层(如氮化硅)的使用可以减少界面陷阱,抑制热载流子效应。研究表明,这些工艺优化可将器件可靠性提升至数千小时以上。

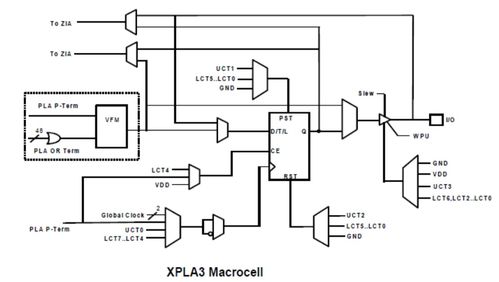

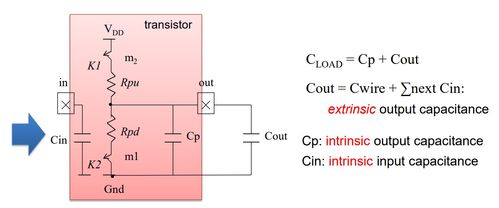

布局与版图设计对抗击穿性能有显著影响。在射频集成电路中,LDMOS往往以多指状结构实现大功率输出,但布局不当会导致局部过热和电场失衡。为应对此,可采用叉指状布局并增加源极金属覆盖,以改善散热和电流分布。另外,添加场板和隔离环是常见技术:场板(如多晶硅或金属延伸)能调制漂移区电场,降低峰值;隔离环(如深N阱)则防止横向击穿和闩锁效应。在版图层面,优化接触孔排列和降低寄生电阻电容也有助于提升整体抗击穿能力。例如,通过仿真工具(如TCAD)进行电场模拟,可指导布局优化,使击穿电压达到理论值的90%以上。

电路级协同设计不容忽视。在射频集成电路中,LDMOS通常嵌入匹配网络和偏置电路中,其抗击穿性能受外围元件影响。采用自适应偏置技术,如温度补偿电路,可动态调整工作点,避免过压应力。集成保护二极管或限流器能在瞬态事件(如ESD)中提供旁路路径。仿真与测试结合是验证设计的关键:通过负载牵引测试和加速寿命试验,可以评估器件在实际射频环境下的抗击穿性能。数据显示,综合优化后,LDMOS在2.4GHz频段下,击穿电压可超过50V,满足5G等高压应用需求。

适用于射频集成电路的抗击穿LDMOS设计是一个多维度工程问题,涉及器件物理、工艺技术和电路集成。通过结合RESURF结构、工艺优化、版图布局以及电路保护策略,可显著提升器件的可靠性和性能。随着新材料(如氮化镓)和三维集成技术的发展,LDMOS设计将进一步演进,为射频集成电路的高功率应用开辟新路径。设计者需持续关注工艺进步和仿真工具更新,以实现更高效、更稳健的抗击穿解决方案。