引言

对于攻读微电子、集成电路等相关专业的国科大学子而言,《超大规模集成电路设计》是一门兼具理论深度与工程实践挑战的核心课程。期末考试不仅是对知识体系的系统检验,更是对设计思维与问题解决能力的综合评估。一份高效的复习计划,能够帮助同学们提纲挈领,从容应考。

一、 核心知识模块梳理

1. VLSI设计流程与设计方法学

这是课程的宏观框架。务必掌握从系统规范、逻辑设计、电路设计、物理设计到制造测试的完整流程。理解自顶向下(Top-Down)与自底向上(Bottom-Up)设计方法,以及它们在现代SoC(片上系统)设计中的融合应用。

2. CMOS制造工艺与版图设计

- 回顾CMOS制造的关键步骤(光刻、刻蚀、离子注入、淀积等)。

- 深入理解设计规则(Design Rules)的内涵,包括线宽、间距、覆盖等约束,并能解读简单的设计规则文件。

- 熟练掌握基本器件(反相器、与非门、或非门)的版图绘制,理解有源区、多晶硅、金属层、接触孔和通孔的作用。

- 掌握“棍棒图”(Stick Diagram)作为连接电路图与版图的桥梁作用。

3. CMOS电路特性与性能分析

- 静态特性:深刻理解电压传输特性(VTC)、噪声容限、开关阈值。

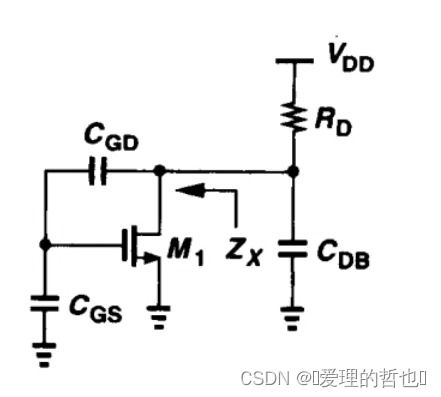

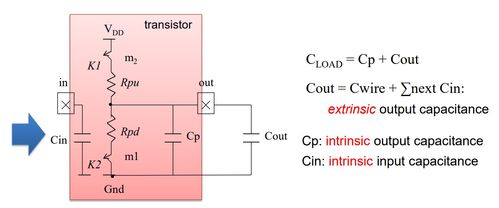

- 动态特性:这是重中之重。熟练掌握延时(传播延时、上升/下降时间)的计算方法,理解其与负载电容、晶体管尺寸(W/L)、电源电压的依赖关系。

- 功耗分析:清晰区分动态功耗、静态功耗(漏电流)和短路功耗的来源与估算公式。低功耗设计技术(如电源门控、多阈值电压技术、动态电压频率调节DVFS)是常考点。

4. 组合逻辑与时序逻辑电路设计

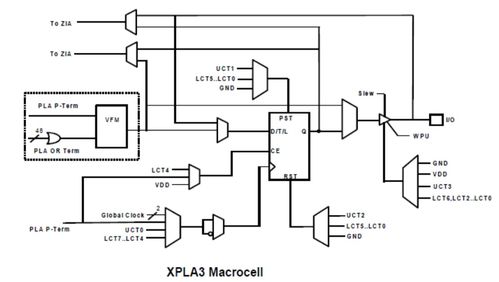

- 组合逻辑:掌握静态CMOS、有比逻辑(如伪NMOS)、传输管逻辑、动态逻辑(Domino逻辑)等不同电路结构的原理、优缺点和典型应用场景。

- 时序逻辑:重点掌握锁存器(Latch)和触发器(Flip-Flop)的电路结构(如传输门结构、主从结构)、工作原理、时序参数(建立时间、保持时间、时钟到输出延时)。

5. 存储器与互连线

- 存储器:了解SRAM(6T单元)和DRAM(1T1C单元)的基本存储单元结构、读写操作原理及外围电路(如灵敏放大器、行列译码器)的作用。

- 互连线:理解互连线寄生参数(电阻R、电容C、电感L)对信号完整性、延时和功耗的影响。掌握Elmore延时模型用于估算RC树网络延时。

6. 设计验证与测试

- 了解功能验证、时序验证、物理验证(DRC, LVS)的基本概念。

- 掌握可测性设计(DFT)中的基本概念,如扫描链(Scan Chain)的原理与插入方法。

二、 复习策略与重点

- 回归教材与课件:以课程指定教材(如Rabaey的《数字集成电路设计》)和课堂PPT为核心,系统回顾每个章节。课件中的例题和推导过程往往是考试重点的映射。

- 攻克计算与分析题:

- 延时计算(反相器链、逻辑门)、功耗估算、噪声容限求解是计算题的常客。务必亲手推导和练习,熟悉公式应用场景。

- 能够分析给定电路图的工作原理、时序特性,并识别潜在问题(如竞争冒险、电荷分享等)。

- 理解版图与电路图的对应关系:能够根据简单的电路图画出对应的“棍棒图”或示意性版图,反之亦然。这是考察空间思维和工艺理解能力的关键。

- 关注设计权衡(Trade-off):VLSI设计的精髓在于在速度(性能)、面积、功耗之间取得平衡。复习时要有意识地将不同技术(如逻辑风格选择、晶体管尺寸缩放)放在这个三维空间中进行对比思考。

- 研习历年真题与作业题:在掌握基础知识后,通过真题模拟考试环境,查漏补缺。重点分析错题,理解背后的原理,而非死记答案。

三、 复习时间建议

- 第一阶段(知识回顾,约1周):按模块通读教材与课件,整理个人笔记,形成知识树。

- 第二阶段(深化理解与练习,约1周):集中攻克重点难点,完成课后习题和作业题,强化计算与分析能力。

- 第三阶段(模拟与冲刺,约3-5天):进行真题模拟,限时完成,检验复习效果。针对薄弱环节进行最后强化,复习所有整理过的公式、概念和设计规则。

##

超大规模集成电路设计是一门充满智慧与创造性的学科。期末考试只是学习过程中的一个节点,其根本目的在于促使大家系统性地构建起从晶体管到复杂系统的设计知识体系。保持清晰的逻辑,注重理解而非死记,将每个知识点置于实际设计的语境中去思考,方能举一反三,游刃有余。预祝各位国科大学子复习顺利,在考场上展现出扎实的学识与卓越的工程素养!