随着集成电路技术向更高密度、更小尺寸和更强性能的方向持续发展,封装设计的重要性日益凸显。它不仅作为芯片与外部世界进行物理连接和电气互连的桥梁,更是影响产品整体可靠性、功耗、散热及信号完整性的关键环节。因此,如何系统性地提升集成电路封装设计的可靠性,已成为业界与学术界共同关注的核心课题。本文旨在探讨提升封装设计可靠性的若干核心方法。

1. 材料选择与匹配性优化

可靠性的基石始于材料。封装涉及基板、键合线、塑封料、底部填充胶、焊球等多种材料。必须根据芯片的功耗、工作频率、热膨胀系数(CTE)以及应用环境(如高温、高湿、高机械应力)来精心选择材料。例如,对于高功率芯片,需选用高导热率的基板材料(如陶瓷或金属基板)和热界面材料(TIM),以确保高效散热,避免因过热导致的性能退化或失效。必须关注材料之间的CTE匹配。如果芯片、基板、塑封料之间的热膨胀系数差异过大,在温度循环过程中会产生巨大的热机械应力,导致界面分层、焊点开裂或硅片破裂。通过材料仿真与实验,优化材料组合,是降低此类应力的根本途径。

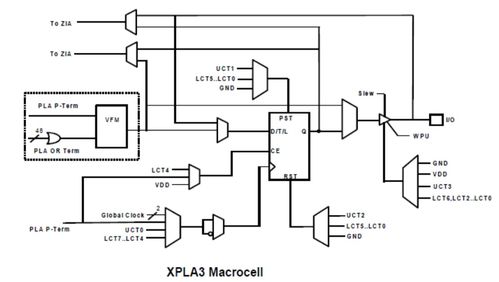

2. 先进封装架构与互连技术应用

传统的引线键合(Wire Bonding)封装在应对高频、高I/O密度芯片时面临挑战。采用系统级封装(SiP)、晶圆级封装(WLP)、2.5D/3D集成等先进架构,可以大幅缩短互连长度,减少寄生效应,提升电性能和可靠性。例如,通过硅通孔(TSV)技术实现的3D堆叠,实现了芯片间的垂直短距离互连,不仅提升了传输速度,也因其结构紧凑而减少了传统长引线可能面临的机械振动和热疲劳风险。倒装芯片(Flip Chip)技术用焊凸点代替键合线,提供了更优的电气性能、更高的I/O密度和更好的散热路径,但其对底部填充工艺的可靠性要求也更高。

3. 多物理场协同仿真与设计

在现代封装设计中,凭借经验已不足以应对复杂的可靠性问题。必须引入并依赖多物理场协同仿真工具,在设计阶段就对潜在风险进行预测和规避。这包括:

- 热仿真:精确模拟芯片和封装在最大工作负载下的温度分布和热流路径,识别热点,优化散热设计(如散热片、热管布局)。

- 机械应力仿真:分析在组装过程、温度循环、机械冲击和振动条件下,封装结构内部的应力应变分布,预测可能发生开裂或分层的薄弱环节。

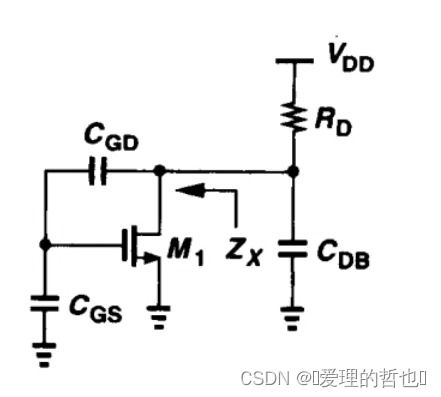

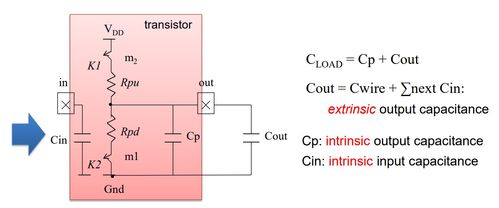

- 电仿真:进行信号完整性(SI)和电源完整性(PI)分析,确保高速信号传输质量,避免因阻抗不匹配、串扰或电源噪声导致的性能不稳定或故障。

通过仿真驱动的设计迭代,可以在昂贵的物理原型制作和测试之前,实现可靠性设计的优化。

4. 工艺控制与制造可靠性

再优秀的设计也需要精密的制造工艺来实现。封装工艺的波动会直接影响最终产品的可靠性。关键工艺控制点包括:

- 焊接/键合工艺:确保焊点或键合点的强度、一致性和无空洞。X射线检测和声学扫描显微镜(C-SAM)是常用的无损检测手段。

- 塑封成型工艺:控制塑封料的流动、固化过程,避免产生孔隙、翘曲或不完全填充,特别是对于具有深窄间隙的复杂结构。

- 清洁与污染物控制:微量的离子污染物(如氯离子、钠离子)可能导致后续使用中的电化学迁移和腐蚀失效。严格的清洁和洁净室环境控制至关重要。

实施统计过程控制(SPC),建立完善的工艺设计规范(DPF)和失效模式与影响分析(FMEA),是保障制造可靠性的系统性方法。

5. 全面的可靠性测试与失效分析

可靠性需要通过标准化的加速寿命测试来验证和量化。常见的测试包括高温存储(HTSL)、温度循环(TCT)、高温高湿偏压(THB)、机械冲击与振动测试等。这些测试旨在在短时间内激发产品在多年使用中可能出现的失效模式。

更为关键的是,当测试中出现失效时,必须进行深入的失效分析(FA)。利用扫描电子显微镜(SEM)、聚焦离子束(FIB)、能量色散X射线光谱(EDX)等先进工具,定位失效点,分析失效机理(如金属电迁移、介电击穿、疲劳断裂等)。失效分析的结论必须反馈至设计和工艺环节,形成“设计-制造-测试-分析-改进”的闭环,从而实现可靠性的持续提升。

结论

集成电路封装设计的可靠性提升是一个贯穿材料科学、结构设计、仿真分析、工艺制造和测试验证的系统工程。它要求设计者具备跨学科的知识,并积极采用先进的技术与工具。随着人工智能和机器学习在仿真优化和缺陷预测中的应用,以及面向更极端环境(如汽车电子、航空航天)的可靠性需求,封装可靠性的研究将不断向更深层次、更智能化方向发展。唯有通过全方位的协同创新与精益求精,才能打造出在复杂严苛环境下仍能稳定运行的“强健”集成电路产品。