专用集成电路(ASIC)设计是现代电子工业的核心与基石,它代表着为特定应用或客户需求而量身定制的芯片设计。与通用处理器(如CPU、GPU)不同,ASIC通过高度优化的硬件结构,在目标领域内实现了无与伦比的性能、能效和成本优势,广泛应用于人工智能加速、加密货币挖矿、通信基础设施、汽车电子及消费电子等领域。

ASIC设计流程是一个复杂且高度系统化的工程,主要包含以下几个关键阶段:

是规格定义与架构设计。这是项目的起点,需要明确芯片的功能、性能指标(如算力、功耗、带宽)、物理接口(如I/O、内存类型)以及目标工艺节点。系统架构师在此阶段进行高层次建模和权衡分析,确定芯片的整体架构、模块划分以及关键算法在硬件上的实现方式。

进入前端设计阶段。设计工程师使用硬件描述语言(如Verilog或VHDL)将架构转化为可综合的寄存器传输级(RTL)代码。这一阶段的核心是功能正确性,需要通过大量的仿真验证来确保RTL代码的行为符合规格定义。形式验证、静态时序分析等工具也被用来辅助检查逻辑等价性和早期时序问题。

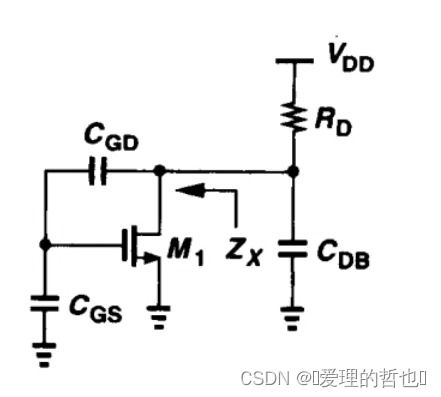

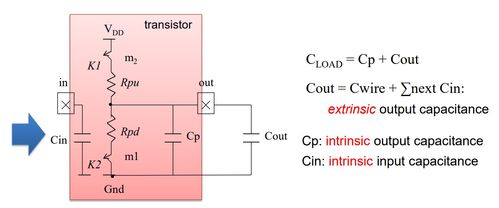

紧接着是后端设计,也称为物理设计。这是将RTL代码“翻译”成实际物理版图的过程。它包括逻辑综合(将RTL转换为基于标准单元库的门级网表)、布局规划、时钟树综合、布线、物理验证(如设计规则检查DRC、版图与电路图一致性检查LVS)以及最终的时序签核和功耗分析。后端设计深度依赖于电子设计自动化(EDA)工具,并与芯片制造厂(Foundry)提供的工艺设计套件(PDK)紧密耦合。

设计完成后,便进入流片与制造环节。将最终确认的版图数据(GDSII格式)提交给晶圆厂进行光刻制造,生产出物理晶圆,再经过切割、封装和测试,最终成为一颗可用的ASIC芯片。首次流片(Tape-out)成本高昂且周期长,因此前期验证的完备性至关重要。

ASIC设计也面临着巨大挑战。其开发成本极高,涉及数百万至数千万美元的NRE(一次性工程费用),且设计周期漫长,通常需要12到36个月。技术风险不容忽视,任何设计缺陷都可能导致流片失败,造成巨大损失。一旦芯片制造完成,其功能便被“固化”,难以像软件一样进行升级修改,灵活性较差。

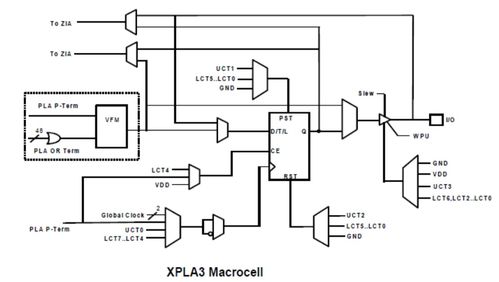

为了平衡定制化与灵活性,业界发展出了如可编程ASIC(如FPGA,可作为ASIC的原型验证平台或用于小批量应用)、基于标准单元的ASIC以及全定制ASIC等多种设计形态。Chiplet(小芯片) 和 异构集成 技术的兴起,为ASIC设计提供了新的范式,允许将不同工艺、不同功能的裸芯片通过先进封装集成在一起,从而在保持性能优势的提升设计灵活性和降低成本。

随着人工智能、5G/6G、自动驾驶等技术的飞速发展,市场对高性能、低功耗专用计算硬件的需求将持续爆发。ASIC设计,作为连接算法创新与物理实现的桥梁,将继续在摩尔定律放缓的后时代,通过架构创新和系统级优化,驱动着整个电子信息产业向前迈进。它不仅是技术的实现,更是战略的抉择,是企业构建核心硬件竞争力的关键所在。