集成电路版图设计作为芯片制造前的关键环节,直接影响着芯片的性能、功耗、面积及可靠性。本文结合eetop.cn论坛中常见的资源《集成电路版图layout设计与cadence讲义.pdf》,简要介绍版图设计的基本概念、设计流程,以及如何使用Cadence工具进行实践。

一、集成电路版图设计概述

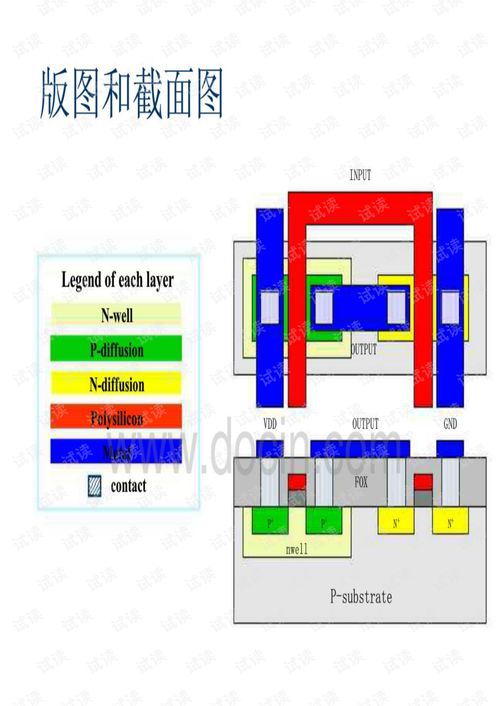

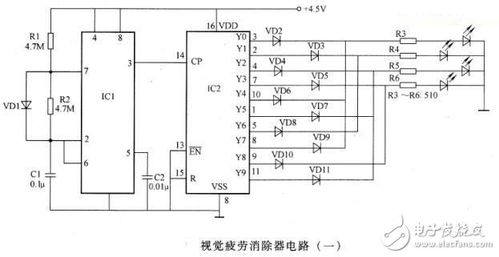

版图设计(Layout Design)是将电路原理图转换为一系列几何图形,这些图形定义了芯片制造中各层材料的形状和位置。设计师需要考虑工艺规则(Design Rule)、电气规则(Electrical Rule)、匹配性、寄生效应等诸多因素,确保设计出的版图既能正确实现电路功能,又满足制造要求。

二、版图设计流程

典型的版图设计流程包括:

- 电路理解与规划:分析电路结构,识别关键路径和敏感模块。

- 布局规划(Floorplan):确定芯片整体布局,规划电源、地线及模块位置。

- 单元布局(Placement):摆放晶体管、电阻、电容等基本单元。

- 布线(Routing):连接各单元,形成互连线。

- 设计规则检查(DRC):确保版图符合制造工艺规则。

- 电路图版图一致性检查(LVS):验证版图与原理图的一致性。

- 寄生参数提取与后仿真:提取版图寄生参数,进行性能验证。

三、Cadence工具在版图设计中的应用

Cadence是业界广泛使用的EDA(电子设计自动化)工具套件,其版图设计工具Virtuoso提供了强大的设计环境。

- 设计输入:通过Virtuoso Schematic Composer绘制电路图,再使用Virtuoso Layout Suite进行版图编辑。

- 版图绘制:提供丰富的图形编辑功能,支持层次化设计,便于复杂模块的管理。

- 验证工具:集成DRC、LVS工具(如Assura或PVS),可高效完成设计验证。

- 技能提升:结合《集成电路版图layout设计与cadence讲义》等资料,可系统学习快捷键操作、匹配设计、抗干扰布局等实用技巧。

四、学习资源与建议

对于初学者,建议:

- 从基础理论入手,理解CMOS工艺和器件物理。

- 结合讲义进行工具实操,熟悉Virtuoso界面和流程。

- 多参考成功案例,分析优秀版图的设计思路。

- 参与eetop.cn等专业论坛的讨论,分享经验,解决问题。

版图设计是一门理论与实践并重的技术,只有通过不断学习和项目实践,才能逐步掌握其精髓,设计出高性能、高可靠性的集成电路。