集成电路(Integrated Circuit, IC)设计是现代电子工业的核心,其过程复杂且精密,涉及从系统架构到物理实现的多个层级。本文将通过图文结合的方式,概述集成电路设计的关键环节与主流工具,并介绍如“熊猫办公”这类资源平台在设计过程中的辅助作用。

一、 集成电路设计流程全景图

一套完整的集成电路设计流程,通常可以形象地通过一系列图表来展示:

- 系统架构与规格定义图:此阶段确定芯片的功能、性能、功耗和成本目标。示意图通常展示顶层模块划分和总线互连结构。

- 前端设计(逻辑设计)示意图:

- RTL(寄存器传输级)代码:以硬件描述语言(如Verilog/VHDL)编写的源代码,是设计的起点。图示常为代码片段与对应电路模块的映射关系。

- 功能仿真波形图:展示信号在仿真环境下的时序变化,验证逻辑正确性。图中包含时钟、复位及各数据信号的变化曲线。

- 综合后网表结构图:将RTL代码映射到标准单元库后的逻辑门级连接图,呈现为网状拓扑结构。

- 后端设计(物理设计)布局图:

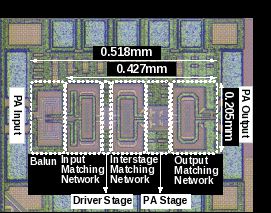

- 布局规划(Floorplan)图:定义芯片核心区域、模块位置、I/O引脚和电源网络的初步布局,形状通常为矩形分区。

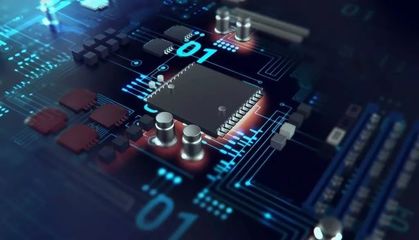

- 布局布线(Place & Route)效果图:展示标准单元(逻辑门)的具体摆放位置以及单元之间多层金属连线的走向,图像色彩丰富,线条密集。

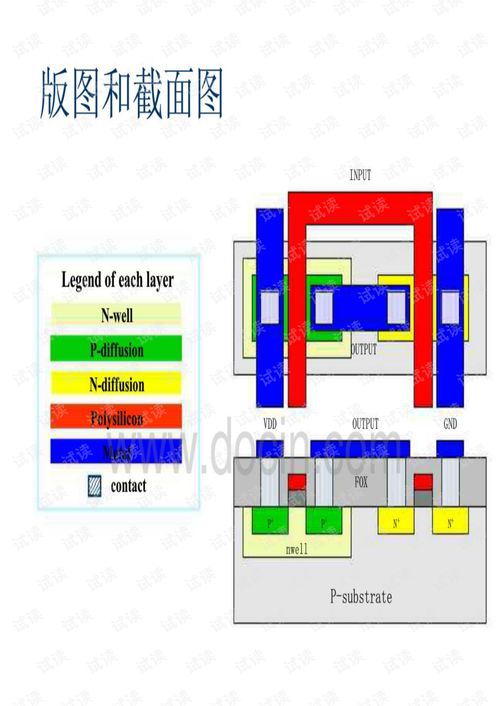

- 版图(Layout)最终图:设计完成的晶体管级几何图形,各层(如扩散层、多晶硅层、金属层)用不同颜色和图案区分,是交付制造的最终数据。

- 物理验证图:包括DRC(设计规则检查)和LVS(版图与电路图一致性检查)的报告示意图,标示出可能存在的规则违反点。

- 验证与测试相关图表:

- 测试向量图:用于芯片制造后测试的输入输出激励模式图。

- 封装结构图:展示芯片裸片(Die)与封装外壳(Package)的连接方式(如引线键合、倒装焊)。

二、 主流设计工具与界面概览

设计过程高度依赖EDA(电子设计自动化)工具,其用户界面和生成的可视化报告是重要的“设计图片”:

- 逻辑综合工具(如Synopsys Design Compiler):界面显示综合约束、面积/时序报告以及优化后的网表结构视图。

- 布局布线工具(如Cadence Innovus, Synopsys IC Compiler):提供交互式的芯片布局视图,设计师可实时调整单元位置、查看布线拥塞热力图(通常用颜色深浅表示拥塞程度)。

- 版图编辑与验证工具(如Cadence Virtuoso, Mentor Calibre):核心界面是层次化的版图编辑器,以及DRC/LVS验证结果的图形化标示。

- 电路仿真工具(如Cadence Spectre, Synopsys HSPICE):输出详细的瞬态、直流或交流分析波形图。

三、 “熊猫办公”等资源平台的辅助角色

“熊猫办公”这类综合性办公素材与模板平台,虽然不提供专业的EDA工具,但能为集成电路设计的相关工作提供有益的素材支持:

- 设计文档与演示制作:设计师在撰写设计文档、项目报告、技术方案或制作答辩PPT时,可以从平台获取:

- 专业的科技、电路主题PPT模板。

- 高质量的电子元件、芯片、流程图、数据图表等矢量图标与插图。

- 统一的项目文档格式模板,提升文档规范性。

- 流程图与架构图绘制:使用平台提供的流程图、组织结构图素材,可以快速绘制系统架构图、设计流程管理图,使沟通更直观。

- 团队协作与知识管理:平台可能提供的项目管理甘特图模板、会议纪要模板等,有助于设计团队进行进度管理和知识沉淀。

值得注意的是,核心的集成电路设计图表(如版图、仿真波形)必须由专业EDA工具生成以确保其准确性和可制造性。而“熊猫办公”等平台提供的素材,主要用于外围的表达、沟通和文档美化工作。

集成电路设计的“图片大全”,实质上是其复杂设计流程与技术内涵的可视化体现。从抽象的代码到具体的几何图形,每一张图表都是设计思想与工程智慧的结晶。理解这些图表,有助于把握芯片设计的精髓。善于利用“熊猫办公”等资源平台来提升设计文档的呈现效果与团队协作效率,也是现代IC设计师一项有价值的辅助技能。